# INTEL Pentium® OverDrive® PROCESSOR

- Powerful CPU Upgrade for Intel486™ CPU-Based Systems

- Makes Intel Procesor-Based Systems

Run Faster

- Significantly Accelerates All Software Applications

- Designed for Systems Based on:

- Intel486™ SX Processors

- Intel486™ DX Processors

- IntelSX2™ Processors

- IntelDX2™ Processors

- Compatible with Installed Base of Thousands of Applications

- Based on Advanced Intel Pentium® Processor Technology

- Incorporates SMM Power Saving Features

The Pentium<sup>®</sup> OverDrive<sup>®</sup> processor upgrades Intel486™ processor-based systems to Pentium processor technology. It features a true Pentium processor core (Superscalar Architecture, Branch Prediction, and faster floating point unit), silicon enhancements (separate code and data caches, 16 KB each, and 32-bit bus interface), and package innovations (on-package voltage regulation and fan heat sink).

port

290544-25

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Information contained herein supersedes previously published specifications on these devices from Intel.

© INTEL CORPORATION, 1995

Order Number: 290544-001

<sup>\*</sup>Other brands and names are the property of their respective owner.

# Intel Pentium® OverDrive® Processor

| <b>CONTENTS</b>                                                                                                                                                                                                                                                      | PAGE              | CONTENTS                                                                                                                                                                                                                                                 | PAGE                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1.0 INTRODUCTION  1.1 Pentium® OverDrive® Processor Product Overview  1.2 Product Description  1.3 Product Description                                                                                                                                               | 6                 | 5.0 SOFTWARE CONSIDERATIO 5.1 External Bus Cycle Ordering 5.1.1 Write Buffers and Memory Ordering                                                                                                                                                        | ı 28<br>ory               |

| 1.3 Purpose of this Document 1.4 Compatibility Note  2.0 Pentium OverDrive PROCESSOR SPECIFICATIONS  2.1 Pentium OverDrive Processor Pinout  2.2 Pin Cross Reference  2.3 Pentium OverDrive Processor Pin Descriptions  2.3.1 Signal Descriptions  2.3.2 Output Pins | 8 8 9 11 11 12 14 | 5.1.2 External Event Synchronization 5.2 Model Specific Registers 5.3 Exception Priorities 5.3.1 External Interrupt Considerations 5.4 BIOS and Software 5.4.1 Pentium OverDrive Production 5.4.2 BIOS Boot Code Assumptions 5.4.3 Timing Dependent Loop |                           |

| 2.3.3 Input Pins                                                                                                                                                                                                                                                     |                   | BIOS                                                                                                                                                                                                                                                     | 30                        |

| 3.0 CACHE FUNCTIONALITY  3.1 Cache Introduction  3.2 Cache Organization  3.3 State Transition Tables                                                                                                                                                                 | 16<br>16<br>17    | 6.0 DIFFERENCES BETWEEN TH INTEL486 FAMILY AND THE POOVERDRIVE PROCESSOR 6.1 Software                                                                                                                                                                    | <b>entium</b><br>30<br>30 |

| 3.3.1 Read Cycle 3.3.2 Write Cycle 3.3.3 Inquire Cycles (Snooping) 3.4 Processor Code Cache Consistency Protocol 3.5 Warm Reset Cache Behavior                                                                                                                       | 19                | 7.0 DIFFERENCES BETWEEN TH Pentium PROCESSOR AND TH Pentium OverDrive PROCESSO 7.1 Software 7.2 Hardware                                                                                                                                                 | JE<br>DR31<br>31          |

| 4.0 HARDWARE DESIGN CONSIDERATIONS  4.1 Introduction 4.1.1 Cache Consistency Cycles 4.1.2 Write Back Cycles                                                                                                                                                          | 21<br>21          | 8.0 TESTABILITY  8.1 Introduction  8.2 Pentium OverDrive Processor Reset Pins/BIST Initiation  8.3 Built In Self Test (BIST)  8.4 Tri-State Test Mode                                                                                                    |                           |

| 4.2 WB/WT# as an Initialization Input  4.3 INIT Functionality  4.4 Instruction Prefetch                                                                                                                                                                              | 26                | 8.5 Cache, TLB and BTB Test Registers  8.6 Fan Protection Mechanism a THermal FRBor Rit                                                                                                                                                                  |                           |

| CONTENTS                                                                           | PAGE  | CONTENTS                                                                                 | PAGE              |

|------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------|-------------------|

| 9.0 MECHANICAL AND ELECTRIC DESIGN CONSIDERATIONS 9.1 Introduction                 | 36    | 10.0 DESIGNING FOR Write-<br>Enhanced IntelDX2/Pention OverDrive PROCESSOR COMPATIBILITY | um                |

| 9.2 Mechanical Design Considerations                                               | 36    | 10.1 Pinout Differences                                                                  |                   |

| 9.2.1 Backward Compatibility                                                       | 36    | 10.1.1 Additional Pins or<br>Pentium OverDrive Pro                                       |                   |

| <ul><li>9.2.2 Physical Dimensions</li><li>9.2.3 Active Heat Sink Details</li></ul> |       | 10.1.2 Pins Not Supporto<br>Pentium OverDrive Pro                                        | ed by the         |

| 9.2.4 Socket 3 Pinout<br>9.2.5 "End User Easy"                                     | 39    | 10.1.3 Shared Signals Lo                                                                 | ocated on         |

| Recommendations                                                                    | 40    | 10.2 Functional Differences                                                              |                   |

| 9.2.6 ZIF Socket Vendors 9.3 Upgrade Circuit Design                                |       | 10.2.1 Write Back Proce Considerations                                                   |                   |

| 9.3.1 Dual Processor Site Des                                                      |       | 10.2.2 Standard/Enhand<br>Differences                                                    | ced Bus           |

| 9.3.2 Single Processor Site Design                                                 | 41    | 10.2.3 Software Differen                                                                 | ces 48            |

| 9.3.3 Circuit Considerations fo<br>Write Back Cache Support                        |       | 10.2.3.1 Cache Testir<br>Registers                                                       | ng and Test<br>48 |

| 9.3.4 Pentium OverDrive Proce                                                      | essor | 10.2.3.2 Timing Loops                                                                    | s 48              |

| Decoupling Capacitors 9.4 Socket Test Requirements .                               |       | 10.2.4 External Snooping<br>Requirements on EAD                                          |                   |

| 9.5 Thermal Management 9.5.1 Thermal Calculations for                              | 41    | 10.2.5 Differences in Sto<br>State Operation                                             |                   |

| Hypothetical System                                                                |       | 11.0 DC/AC SPECIFICATION                                                                 | <b>IS</b> 49      |

| 9.5.2 Airflow                                                                      | 42    | 11.1 DC Specifications                                                                   | 50                |

|                                                                                    |       | 11.2 AC Specifications                                                                   | 51                |

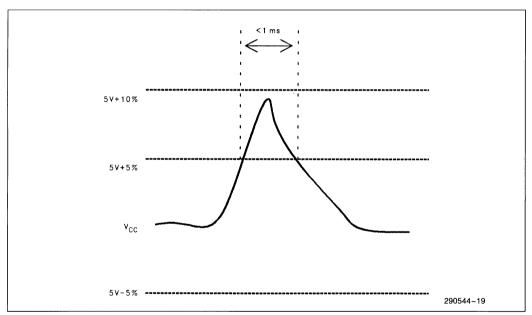

|                                                                                    |       | 11.2.1 V <sub>CC</sub> Transient<br>Specification                                        | 51                |

|                                                                                    |       | 11.2.2 Derating I/O Specifications                                                       | 57                |

| CONTEN      | NTS                                                         | PAGE |

|-------------|-------------------------------------------------------------|------|

| FIGURES     |                                                             |      |

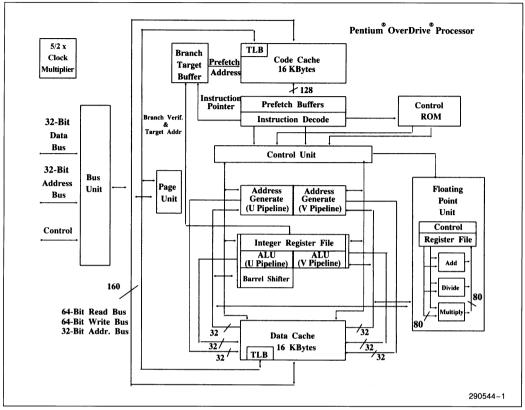

| Figure 1-1  | Pentium® OverDrive® Processor Block Diagram                 | 7    |

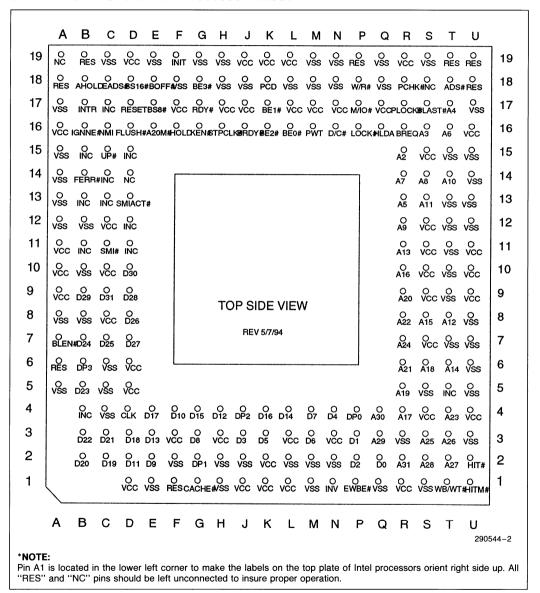

| Figure 2-1  | Pentium OverDrive Processor Pinout (Top Side View)          | 9    |

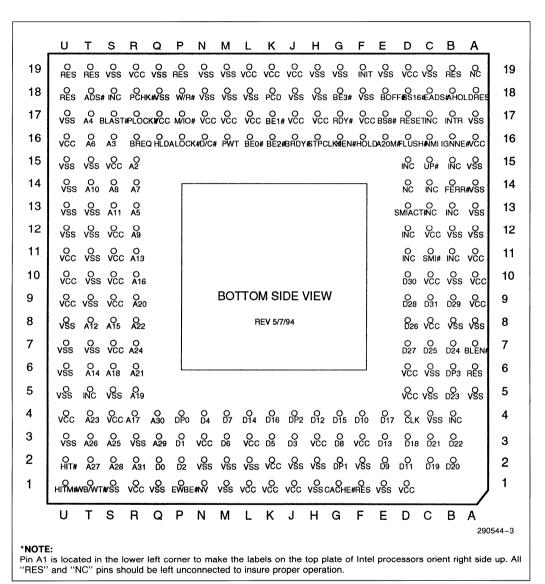

| Figure 2-2  | Pentium OverDrive Processor Pinout (Bottom Side View)       |      |

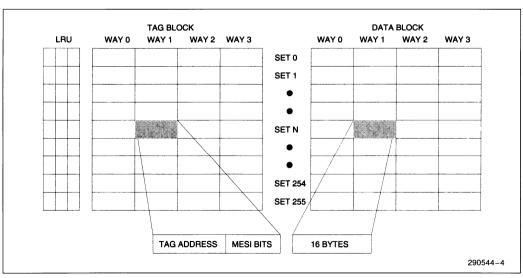

| Figure 3-1  | Conceptual Organization of Data Cache                       |      |

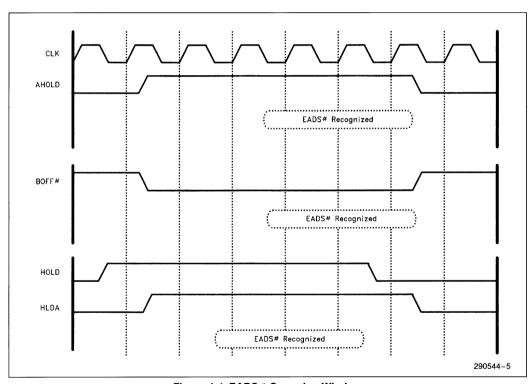

| Figure 4-1  | EADS# Snooping Window                                       |      |

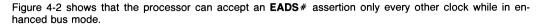

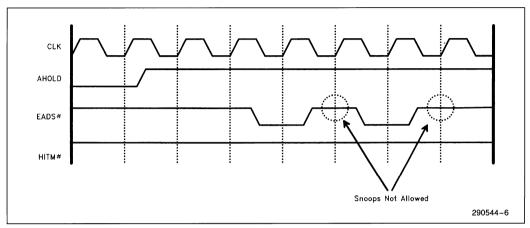

| Figure 4-2  | EADS# Snooping Frequency in Enhanced Bus Mode               |      |

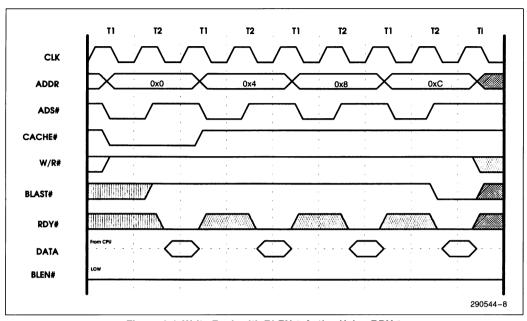

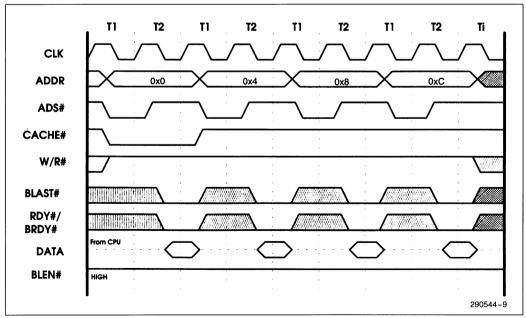

| Figure 4-3  | Write Back Operation—BLEN# Active                           | 24   |

| Figure 4-4  | Write Back with BLEN# Active But Using RDY#                 |      |

| Figure 4-5  | Write Back as Four 4 Byte Transfers (BLEN# Inactive)        |      |

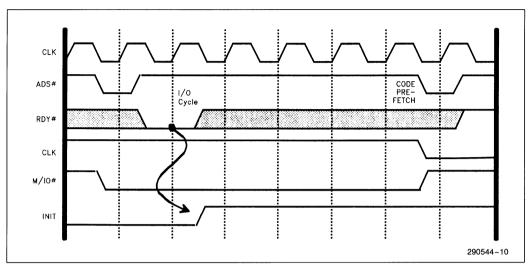

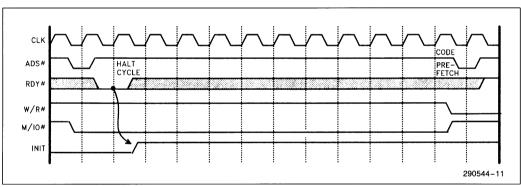

| Figure 4-6  | ADS# Issued during INIT: Case 1                             |      |

| Figure 4-7  | ADS# Issued during INIT: Case 2                             |      |

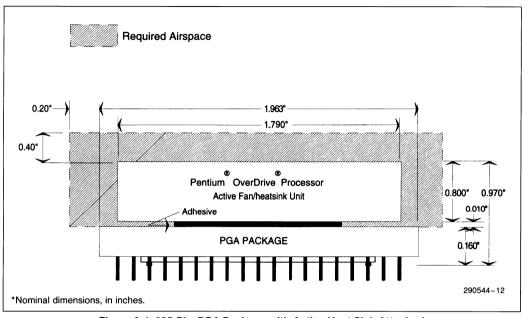

| Figure 9-1  | 235-Pin, PGA Package with Active Heat Sink Attached         |      |

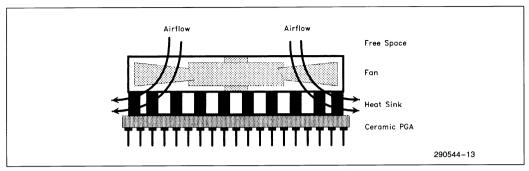

| Figure 9-2  | Active Heat Sink Example                                    | 38   |

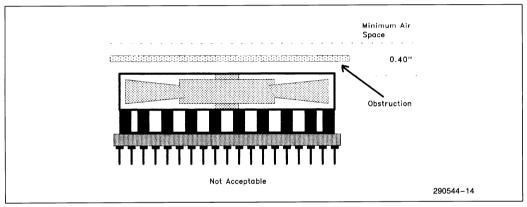

| Figure 9-3  | Active Heat Sink Top Space Requirements                     | 38   |

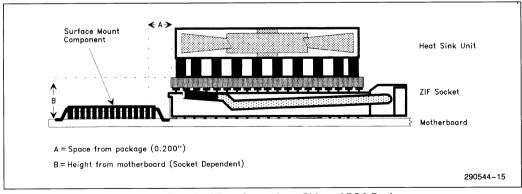

| Figure 9-4  | Required Free Space from Sides of PGA Package               | 38   |

| Figure 9-5  | 237-Pin PGA ZIF Socket 3                                    | 39   |

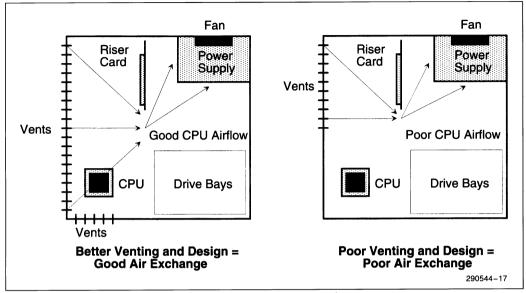

| Figure 9-6  | Pentium OverDrive Processor Airflow Design Examples         | 43   |

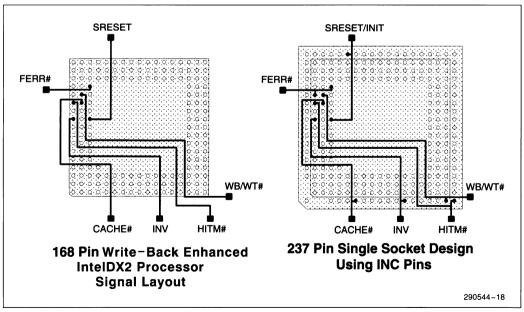

| Figure 10-1 | Sample Routing of INC Pins                                  | 46   |

| Figure 11-1 | V <sub>CC</sub> Transient Example                           | 51   |

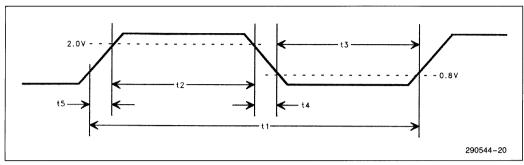

| Figure 11-2 | CLK Waveform                                                | 56   |

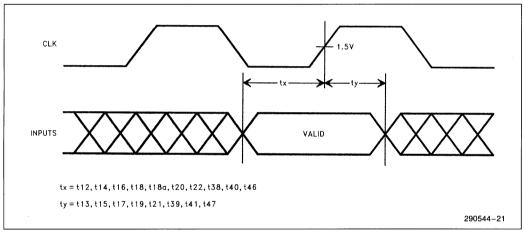

| Figure 11-3 | Setup and Hold Timings                                      | 56   |

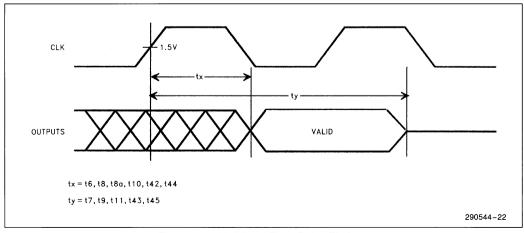

| Figure 11-4 | Valid and Float Delay Timings                               | 56   |

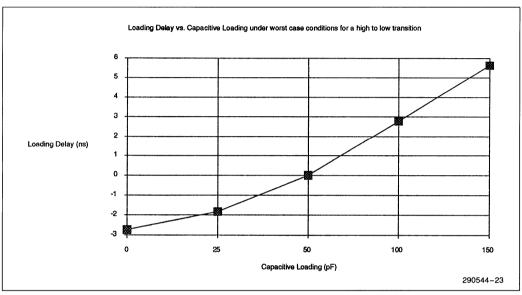

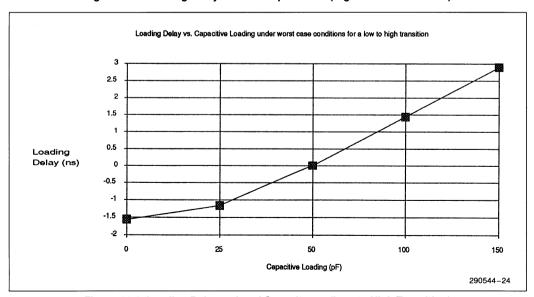

| Figure 11-5 | Loading Delay vs. Load Capacitance (High to Low Transition) | 57   |

| Figure 11-6 | Loading Delay vs. Load Capacitance (Low to High Transition) | 57   |

| CONTE      | NTS                                                                                         | PAGE |

|------------|---------------------------------------------------------------------------------------------|------|

| TABLES     |                                                                                             |      |

| Table 2-1  | Pentium® OverDrive® Processor Pin Cross Reference                                           | 11   |

| Table 2-2  | Signal Description                                                                          | 12   |

| Table 2-3  | Output Pins                                                                                 | 14   |

| Table 2-4  | Input Pins                                                                                  | 15   |

| Table 2-5  | Input/Output Pins                                                                           | 16   |

| Table 3-1  | Data Cache State Transitions for Pentium OverDrive Processor Initiated Unlocked Read Cycles | 18   |

| Table 3-2  | Data Cache State Transitions for Pentium OverDrive Processor Initiated Write Cycles         | 19   |

| Table 3-3  | Cache State Transitions during Inquire Cycles                                               | 20   |

| Table 4-1  | Snoop Cycles under AHOLD, BOFF#, or HLDA                                                    | 21   |

| Table 4-2  | Effects of WB/WT# Initialization                                                            | 26   |

| Table 7-1  | Feature Bit Assignment                                                                      | 31   |

| Table 8-1  | Pentium OverDrive Processor RESET Modes                                                     | 32   |

| Table 8-2  | Register State after RESET, INIT and BIST                                                   | 33   |

| Table 9-1  | Pentium OverDrive Processor, 235-Pin, PGA Package Dimensions with Active Heat Sink Attached | 36   |

| Table 9-2  | Socket and Layout Considerations                                                            | 40   |

| Table 9-3  | Thermal Resistance (°C/W) $\theta_{SI}$                                                     | 42   |

| Table 9-4  | Pentium OverDrive Processor Typical and Maximum I <sub>CC</sub> Values                      | 42   |

| Table 10-1 | Additonal Pentium OverDrive Processor Pins                                                  | 44   |

| Table 10-2 | Additional V <sub>CC</sub> and V <sub>SS</sub> Pins                                         | 45   |

| Table 10-3 | Unsupported Write-Back Enhanced IntelDX2 Pins                                               | 45   |

| Table 10-4 | Single Socket Compatibility Signals                                                         | 46   |

| Table 10-5 | Differences in Cache Cycles                                                                 | 47   |

| Table 10-6 | Differences in Bus Modes                                                                    | 48   |

| Table 11-1 | Absolute Maximum Ratings                                                                    | 50   |

| Table 11-2 | DC Parametric Values                                                                        | 50   |

| Table 11-3 | Pentium OverDrive Processor—25 MHz AC Characteristics                                       | 52   |

| Table 11-4 | Pentium OverDrive Processor—33 MHz AC Characteristics                                       | 54   |

This Specification should be used in conjunction with the *Intel486 Microprocessor Family Data Book* (Order Number 242202-002).

#### 1.0 INTRODUCTION

This data sheet describes the Intel Pentium Over-Drive processor, a CPU upgrade for most Intel486 SX, Intel486 DX, IntelSX2, and IntelDX2 processorbased systems. This processor upgrade will significantly accelerate all software applications run on your existing system, thereby increasing the overall performance of your PC.

It is important to note that this data sheet is intended to be used in conjunction with the *Intel486 Microprocessor Family Databook* (242202-002). Only information which is not in the databook will be included in this datasheet.

# 1.1 Pentium® OverDrive® Processor Product Overview

The Pentium OverDrive processor is the highest performance CPU upgrade available for systems based on the Intel486 family of CPUs. It brings Pentium processor technology (including Superscalar Architecture, Branch Prediction, faster floating-point unit, and separate data and code caches) to Intel486 processor-based systems.

Inclusion of the Pentium OverDrive processor socket in systems based on the Intel486 family of microprocessors provides the end user with an easy and cost-effective way to increase system performance. The majority of upgrade installations which take advantage of the Pentium OverDrive processor socket will be performed by end users and resellers. Therefore, it is important that the design be "end user easy", and that the amount of training and technical expertise required to install the OverDrive processors be minimized. Upgrade installation instructions should be clearly described in the system user's manual. In addition, by making installation simple and foolproof, PC manufacturers can reduce the risk of system damage, warranty claims and service calls. Feedback from Intel's upgrade customers highlight three main characteristics of end user easy designs: accessible socket location, clear indication of upgrade component orientation, and minimization of insertion force. Recommendations regarding designing for easy upgradability appear in Section 9.

# 1.2 Product Description

The Pentium OverDrive processor is designed to upgrade systems based on Intel486 SX, Intel486 DX, IntelSX2, and IntelDX2 processor-based systems and is based on Intel's Pentium processor technology. It is 100% binary compatible with the 8086/88, 80286, Intel386 DX, Intel386 SX, Intel486 DX, Intel486 SX, IntelSX2, and the IntelDX2 processor family.

The Pentium OverDrive processor provides significant improvements over the Intel486 CPU including:

- Superscalar Architecture

- · Dynamic Branch Prediction

- Pipelined Floating-Point Unit

- Separate 16K Code and 16K Data Caches

- Improved Instruction Execution Times

- Write back MESI Protocol implemented in Data Cache

- System Management Mode

The Pentium OverDrive processor significantly increases the integer performance, and can attain up to 2x floating-point performance relative to an equivalent frequency IntelDX2 processor. The initial target bus frequencies for the Pentium OverDrive processor are 25 MHz and 33 MHz.

Figure 1-1 shows the Pentium OverDrive processor's two pipelines and floating-point unit that are capable of independent operation. Each pipeline issues frequently used instructions in a single clock. Together, the dual pipes can issue two integer instructions in one clock, or one floating point instruction (under certain circumstances, 2 floating point instructions) in one clock.

Figure 1-1. Pentium® OverDrive® Processor Block Diagram

The floating-point unit has been completely redesigned over the IntelDX2 processor. Faster algorithms provide at least 3X internal speed-up for common floating point operations including ADD, MUL, and LOAD. With instruction scheduling and overlapped (pipelined) execution, these three performance enhancements can allow many math intensive applications to achieve a 2X performance boost.

The Pentium OverDrive processor implements 32-bit address and data busses.

The block diagram shows that the Pentium OverDrive processor contains two instruction pipelines, the "u" pipe and the "v" pipe. Both the u- and the v-pipes execute integer instructions, while only the u-pipe executes floating point instructions. The one exception is the FXCH instruction which may also be executed in the v-pipe. Therefore, the Penti-

um OverDrive processor is capable of executing two integer instructions in each clock, or one floating point instruction in each clock. Floating point instructions can be paired in certain conditions<sup>(1)</sup>. Each pipeline has its own address generation logic, arithmetic logic unit and data cache interface.

#### NOTE:

1. Refer to the *Pentium Processor Data Book* for more information on instruction execution timing and pairing.

Note that there are two separate caches, a code cache and a data cache. The data cache has three tag ports, one for each of the two pipes and one dedicated to handle snoops from other processors. It has a dedicated Translation Lookaside Buffer (TLB) to translate linear addresses to the physical addresses used by the data cache.

### INTEL Pentium® OverDrive® PROCESSOR

The code cache, branch target buffer and prefetch buffers are responsible for getting raw instructions into the execution units of the Pentium OverDrive processor. Instructions are fetched from the code cache or from the external bus. Branch addresses are remembered by the branch target buffer. The code cache TLB translates linear addresses to physical addresses used by the code cache.

The decode unit decodes the prefetched instructions so that the Pentium OverDrive processor can execute the instruction. The control ROM contains the microcode which controls the sequence of operations that must be performed to implement the Pentium OverDrive processor architecture. The control ROM unit has direct control over both pipelines.

# 1.3 Purpose of this Document

This document describes the system architecture and physical environment of the Pentium OverDrive processor. It also outlines differences between the Intel486 Family of processors and the Pentium OverDrive processor.

# 1.4 Compatibility Note

In this document, some register bits are shown as "Intel Reserved" (RES) and some pins are marked as "No Connects" (NC) or "Reserved" (RES). When reserved bits are called out, treat them as fully undefined. This is essential for software compatibility with future processors. When a pin is marked as a "NC" or "RES" it is important to not connect any other signals to such pins to ensure proper operation. Intel strongly recommends that you follow the guidelines below:

- Do not depend on the states of any undefined bits when testing the values of defined register bits. Mask them out when testing.

- Do not depend on the states of any undefined bits when storing them to memory or another register.

- Do not depend on the ability to retain information written into any undefined bits.

- When loading registers always load the undefined bits as zeros.

- Never connect signals to device pins marked as "NC" or "RES"

- 6) INC Pins are defined as Internal No-Connects. This means that the pin is not connected to the processor internally. Since the pin is inert and floating, it may be used in any manner seen fit, but must meet the INC pin specifications. In general, all INC pins have an intended use to implement a single processor socket system design. The INC pin will never be used for any other function.

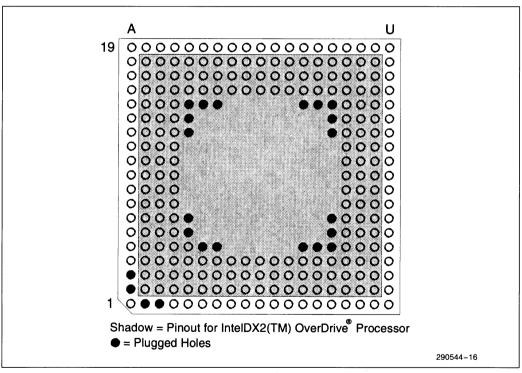

# 2.0 Pentium® OverDrive® PROCESSOR SPECIFICATIONS

The Intel Pentium OverDrive processor socket specifies 237 contacts. The 237 contacts correspond to a standard 240 pin socket with one inside "KEY" contact, one outer "KEY" contact and four 'orientation' contacts plugged on the outside corner. The Pentium OverDrive processor itself (not the socket) does not have any "KEY" pins. The five contacts plugged on the outside corner ensure proper orientation for the Pentium OverDrive processor. The Pentium OverDrive processor pinout is shown in Figures 2-1 and 2-2.

Please note that the boundary scan pins (TCK, TDO,TDI, and TMS), and all testability pins have been removed from the production version of the Pentium OverDrive processor. An engineering sample will be available that will allow the use of boundary scan and testability functions. For more information on boundary scan and testability pins, please contact Intel.

### 2.1 Pentium® OverDrive® Processor Pinout

Figure 2-1. Pentium® OverDrive® Processor Pinout (Top Side View)

Figure 2-2. Pentium® OverDrive® Processor Pinout (Bottom Side View)

### 2.2 Pin Cross Reference

Table 2-1. Pentium® OverDrive® Processor Pin Cross Reference

| Δdd | ress | Data Control N/C V <sub>CC</sub> V |     |        |     |         | ss  |     |     |     |     |     |

|-----|------|------------------------------------|-----|--------|-----|---------|-----|-----|-----|-----|-----|-----|

|     | 1    |                                    |     |        |     |         |     |     |     |     |     |     |

| A2  | R15  | D0                                 | Q2  | A20M#  | E16 | INV     | N1  | A19 |     | L1  | A5  | M18 |

| A3  | S16  | D1                                 | P3  | ADS#   | T18 | KEN#    | G16 | D14 | A9  | L3  | A8  | M19 |

| A4  | T17  | D2                                 | P2  | AHOLD  | B18 | LOCK#   | P16 |     | A10 | L17 | A12 | N2  |

| A5  | R13  | D3                                 | J3  | BE0#   | L16 | M/IO#   | P17 | INC | A11 | L19 | A13 | N18 |

| A6  | T16  | D4                                 | N4  | BE1#   | K17 | NMI     | C16 | D44 | A16 | M17 | A14 | N19 |

| A7  | R14  | D5                                 | КЗ  | BE2#   | K16 | PCD     | K18 | B11 | C8  | N3  | A15 | Q1  |

| A8  | S14  | D6                                 | МЗ  | BE3#   | G18 | PCHK#   | R18 | B13 | C10 | N17 | A17 | Q18 |

| A9  | R12  | D7                                 | M4  | BLAST# | S17 | PLOCK#  | R17 | B4  | C12 | Q17 | B8  | Q19 |

| A10 | T14  | D8                                 | G3  | BLEN#  | A7  | PWT     | M16 | B15 | D1  | R1  | B10 | R3  |

| A11 | S13  | D9                                 | E2  | BOFF#  | E18 | RDY#    | G17 | C17 | D5  | R19 | B12 | S1  |

| A12 | T8   | D10                                | F4  | BRDY#  | J16 | RESET   | D17 | C13 | D6  | S4  | C4  | S5  |

| A13 | R11  | D11                                | D2  | BREQ   | R16 | SMI#    | C11 | C14 | D19 | S7  | C5  | S19 |

| A14 | T6   | D12                                | H4  | BS8#   | E17 | SMIACT# | D13 | D11 | F3  | S9  | C6  | T7  |

| A15 | S8   | D13                                | E3  | BS16#  | D18 | STPCLK# | H16 | D12 | F17 | S10 | C19 | T9  |

| A16 | R10  | D14                                | L4  | CACHE# | G1  | UP#     | C15 | D15 | H3  | S11 | E1  | T10 |

| A17 | R4   | D15                                | G4  | CLK    | D4  | W/R#    | P18 | S18 | H17 | S12 | E19 | T11 |

| A18 | S6   | D16                                | K4  | D/C#   | N16 | WB/WT#  | T1  | T5  | J1  | S15 | F2  | T12 |

| A19 | R5   | D17                                | E4  | DP0    | P4  |         |     |     | J17 | U4  | F18 | T13 |

| A20 | R9   | D18                                | D3  | DP1    | G2  |         |     |     | J19 | U9  | G19 | T15 |

| A21 | R6   | D19                                | C2  | DP2    | J4  |         |     |     | K1  | U10 | H1  | U3  |

| A22 | R8   | D20                                | B2  | DP3    | B6  |         |     | RES | K2* | U11 | H2  | U5  |

| A23 | T4   | D21                                | C3  | EADS#  | C18 |         |     | A6  | K19 | U16 | H18 | U6  |

| A24 | R7   | D22                                | B3  | EWBE#  | P1  |         |     | A18 |     |     | H19 | U7  |

| A25 | S3   | D23                                | B5  | FERR#  | B14 |         |     | 1   |     |     | J2  | U8  |

| A26 | T3   | D24                                | B7  | FLUSH# | D16 |         |     | B19 |     |     | J18 | U12 |

| A27 | T2   | D25                                | C7  | HIT#   | U2  |         |     | F1  |     |     | L2  | U13 |

| A28 | S2   | D26                                | D8  | HITM#  | U1  |         |     | P19 |     |     | L18 | U14 |

| A29 | Q3   | D27                                | D7  | HLDA   | Q16 |         |     | T19 |     |     | M1  | U15 |

| A30 | Q4   | D28                                | D9  | HOLD   | F16 |         |     | U18 |     |     | M2  | U17 |

| A31 | R2   | D29                                | В9  | IGNNE# | B16 |         |     | U19 |     |     |     |     |

|     |      | D30                                | D10 | INIT   | F19 |         |     |     |     |     |     |     |

|     |      | D31                                | C9  | INTR   | B17 |         |     |     |     |     |     |     |

<sup>\*</sup>If designing for single socket compatibility with future Pentium OverDrive processors, pin K2 may be connected to V<sub>CC</sub> via a circuit to limit the current through the pin. Please contact Intel for more information about compatibility with future Pentium OverDrive processors.

# 2.3 Pentium® OverDrive® Processor Pin Descriptions

This section provides a summary of the Pentium OverDrive processor pins and how they function. For

more information on the pinout differences between the Write-Back Enhanced IntelDX2 processor and the Pentium OverDrive processor, please see Section 10.

PRELIMINARY 11

### 2.3.1 SIGNAL DESCRIPTIONS

Table 2-2 provides a brief pin description.

Table 2-2. Signal Description

|          |       | Table 2-2. Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol   | Type  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INTERRUP | TS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INIT     | I     | The INIT pin is the Pentium OverDrive processor initialization pin. Since the SL-enhanced Intel486 processors implement this functionality on the SRESET pin, the corresponding pin (D11) on the Pentium OverDrive Processor is defined as an INC pin so that pin F19 and pin D11 may be tied together on the motherboard. INIT will force the Pentium OverDrive Processor to begin execution in a known state. The processor state after INIT is the same as the state after RESET except that the internal caches, floating point registers, and the SMM base register retain whatever values they had prior to INIT. INIT may NOT be used in lieu of RESET after power-up. INIT can not be used to cause the processor to enter BIST or Tri-State Test Mode. INIT is an edge triggered interrupt and is processed at instruction boundaries. Since INIT is an interrupt, ADS# may be driven even if INIT is active. Recognition of INIT is guaranteed in a specific clock if it is asserted synchronously and meets setup and hold times. To guarantee recognition if INIT is asserted asynchronously, it must have been deasserted for a minimum of two clocks before being returned active to the processor and remain asserted for a minimum pulse width of two clocks. INIT must remain active for three clocks prior to the BRDY# or RDY# of I/O write cycle to guarantee the processor recognizes and performs INIT right after I/O write instruction. INIT is asynchronous but must meet setup and hold times t <sub>20</sub> and t <sub>21</sub> to be recognized on any one clock. INIT is supplied with an internal pull-down. |

| CACHE CO | NTROL |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| WB/WT#   | l     | This pin allows a cache line to be defined as write back or write through on a line by line basis. As a result, it controls the MESI state that the line is saved in. This pin is sampled in the clock in which the first BRDY# or RDY# is returned for a read cycle or a write through cycle. However, it must the meet setup and hold times at every clock. Cache lines are not allocated on write through cycles. This pin is also used as a configuration pin at the falling edge of RESET only. If WB/WT# is driven low, or left unconnected, the processor will operate in a standard bus (write through only) mode. This means that the Pentium OverDrive processor will run in an InteIDX2 processor compatible write through only cache mode. If WB/WT# is driven high, the processor will operate in enhanced bus (write back) mode. INIT can not be used to change the mode of the processor with WB/WT#. During RESET, WB/WT# should be held at its desired value for two clocks before and after the falling edge of RESET. WB/WT# is ignored when the processor is in standard bus mode. Please see Section 3 for a detailed description of the two modes of operation. WB/WT# has an internal pull down resistor to force the processor into the standard bus mode if left unconnected. The pin timings must meet setup and hold times t <sub>38</sub> and t <sub>39</sub> on every clock edge.                                                                                                                                                                                                                              |

Table 2-2. Signal Description (Continued)

|               | Table 2-2. Signal Description (Continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|---------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol        | Туре                                      | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| CACHE INQUIRE |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EWBE#         | I                                         | The External Write Buffer Empty pin, when inactive (HIGH), indicates that a write through cycle is pending in the external system. When the processor generates a non-write back cycle, and EWBE# is sampled inactive, the processor will hold off all subsequent writes to all E- or M- state lines until all write-through cycles have completed, as indicated by EWBE# going active. This ensures that writes are visible from outside the processor in the same order as they were generated by software. When the Pentium OverDrive processor serializes instruction execution through the use of a serializing instruction, it waits for EWBE# to go active before fetching and executing the next instruction. EWBE# is sampled with each BRDY# or RDY# of a write through cycle. If sampled inactive, the processor will repeatedly sample EWBE# in each clock until it is found active. Once sampled active, it will ignore EWBE# until the next BRDY# or RDY# of a write cycle. EWBE# is not sampled and has no effect on processor operation while the processor is in standard bus mode. If unused, EWBE# should be tied LOW or left unconnected. EWBE# is active low and must meet setup and hold times t <sub>38</sub> and t <sub>39</sub> and is supplied with an internal pull-down. |  |  |  |  |

| HIT#          | 0                                         | This pin participates in an inquire cycle. If an inquire cycle hits a valid line in the processor, this pin is asserted two clocks after <b>EADS</b> # has been driven to the processor. If the inquire cycle misses in the processor cache, this pin is negated two clocks after <b>EADS</b> #. This pin changes its value only as a result of inquire cycle as described above and retains its value between any two inquire cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| HITM#         | 0                                         | HITM# is asserted when an inquire cycle hits a modified line in the Pentium OverDrive processor. It can be used to inhibit another bus master from accessing the data until the line is completely written back. HITM# is asserted two clocks after an EADS# assertion hits a modified line in the processor cache and deasserts after the last BRDY# or RDY# of the corresponding write back is returned. HITM# is guaranteed to be deasserted before the ADS# following a write back cycle. If an INVD instruction occurs at the same time as an external snoop, HITM# may be asserted and deasserted without a corresponding ADS# for a write back cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| CACHE BU      | IRST CO                                   | NTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| BLEN#         | l                                         | BLEN# controls if write back cycles will be attempted to run as burst cycles. When BLEN# is HIGH, the processor will write out a dirty line as four separate writes, each with its own ADS# and BLAST#. When BLEN# is LOW, a write back is done as a 16 byte burst. Since BLEN# is a constant input, meaning that it will have to be tied HIGH or LOW. As a result, it does not have setup and hold time specifications. BLEN# is has no effect and is not sampled when the processor is in standard bus mode. BLEN# is supplied with an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| CACHE#        | 0                                         | The CACHE# pin is used to indicate a cache operation. CACHE# will be active along with the first ADS# until the first RDY#/BRDY# and is undefined during any other time period. On cacheable read accesses, CACHE# will be asserted when PCD is low, except on locked cycles. CACHE# will always be asserted in the beginning of cacheable reads (line fills and code prefetches) and can be used as an indication that the processor intends to perform a linefill. For write cycles, CACHE# is active for write backs only. The beginning of a replacement write back can be uniquely identified by the presence of ADS#, W/R# and CACHE# together. The beginning of a snoop write back is marked by ADS#, W/R#, CACHE# and HITM# being active together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

Table 2-2. Signal Description (Continued)

|          |        | rano 2 21 digital 2 dadripulati (continuada)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol   | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OEM CPU  | INTERF | ACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| UP#      | 0      | The <i>upgrade present</i> pin is used to signal the system OEM microprocessor to float its outputs and stop driving the bus. It is active low and is never floated. <b>UP</b> # is driven low at power-up and remains active for the entire duration of the Pentium OverDrive processor operation.                                                                                                                                                                                                                                                    |

| INC PINS |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INC      |        | The <b>INC</b> pin is defined to be an <i>internal no-connect</i> . This means that the pin is not connected internally, and may be used for the routing of external signals. It will never be used for any other function, and is guaranteed to remain an <b>INC</b> pin. Any voltage level applied to an <b>INC</b> pin must remain within the processor V <sub>CC</sub> specifications. Most <b>INC</b> pins have a specified use in creating a design that supports multiple processors in one socket. For more information, please see Section 9. |

### 2.3.2 OUTPUT PINS

Table 2-3 lists all the output pins, indicating their active level, and when they are floated.

Table 2-3. Output Pins

| Name              | Active<br>Level | When Floated                       |

|-------------------|-----------------|------------------------------------|

| BREQ              | HIGH            |                                    |

| HLDA              | HIGH            |                                    |

| BE3#-BE0#         | LOW             | Bus Hold, Backoff                  |

| PWT, PCD          | HIGH            | Bus Hold, Backoff                  |

| W/R#, D/C#, M/IO# | LOW             | Bus Hold, Backoff                  |

| LOCK#             | LOW             | Bus Hold, Backoff                  |

| PLOCK#            | LOW             | Bus Hold, Backoff                  |

| ADS#              | LOW             | Bus Hold, Backoff                  |

| BLAST#            | LOW             | Bus Hold, Backoff                  |

| PCHK#             | LOW             |                                    |

| FERR#             | LOW             |                                    |

| SMIACT#           | LOW             |                                    |

| A3-A2             | HIGH            | Bus Hold, Address Hold and Backoff |

| HIT#, HITM#       | LOW             |                                    |

| CACHE#            | LOW             | Bus Hold, Backoff                  |

| UP#               | LOW             |                                    |

### 2.3.3 INPUT PINS

Table 2-4 lists all input pins, indicating their active level, and whether they are synchronous or asynchronous inputs.

Table 2-4. Input Pins

| Table 2-4. Input Pills |                 |                              |                      |                    |  |  |

|------------------------|-----------------|------------------------------|----------------------|--------------------|--|--|

| Name                   | Active<br>Level | Synchronous/<br>Asynchronous | Internal<br>Resistor | Qualified          |  |  |

| CLK                    |                 |                              |                      |                    |  |  |

| RESET                  | HIGH            | Asynchronous                 |                      |                    |  |  |

| HOLD                   | HIGH            | Synchronous                  |                      |                    |  |  |

| AHOLD                  | HIGH            | Synchronous                  | PULLDOWN             |                    |  |  |

| EADS#                  | LOW             | Synchronous                  | PULLUP               |                    |  |  |

| BOFF#                  | LOW             | Synchronous                  | PULLUP               |                    |  |  |

| FLUSH#                 | LOW             | Asynchronous                 | PULLUP               |                    |  |  |

| A20M#                  | LOW             | Asynchronous                 | PULLUP               |                    |  |  |

| BS16#, BS8#            | LOW             | Synchronous                  | PULLUP               |                    |  |  |

| KEN#                   | LOW             | Synchronous                  | PULLUP               |                    |  |  |

| RDY#                   | LOW             | Synchronous                  |                      |                    |  |  |

| BRDY#                  | LOW             | Synchronous                  | PULLUP               |                    |  |  |

| INTR                   | HIGH            | Asynchronous                 |                      |                    |  |  |

| NMI                    | HIGH            | Asynchronous                 |                      |                    |  |  |

| IGNNE#                 | LOW             | Asynchronous                 | PULLUP               |                    |  |  |

| BLEN#                  | LOW             | Tie High or Low              | PULLUP               |                    |  |  |

| EWBE#                  | LOW             | Synchronous                  | PULLDOWN             | BRDY#/RDY#         |  |  |

| INIT                   | HIGH            | Asynchronous                 | PULLDOWN             |                    |  |  |

| INV                    | HIGH            | Synchronous                  | PULLUP               | EADS#              |  |  |

| STPCLK#                | LOW             | Asynchronous                 | PULLUP               |                    |  |  |

| SMI#                   | LOW             | Asynchronous                 | PULLUP               |                    |  |  |

| WB/WT#                 | вотн            | Synchronous                  | PULLDOWN             | FIRST<br>RDY#/RDY# |  |  |

PRELIMINARY 15

#### 2.3.4 INPUT/OUTPUT PINS

Table 2-5 lists all the input/output pins, indicating their active level, and when they are floated.

Table 2-5. Input/Output Pins

| Name        | Active<br>Level | When Floated                  |

|-------------|-----------------|-------------------------------|

| D31-D0      | HIGH            | Bus Hold, Backoff             |

| DP3-DP0     | HIGH            | Bus Hold, Backoff             |

| A31-A4 HIGH |                 | Bus, Address Hold,<br>Backoff |

### 3.0 CACHE FUNCTIONALITY

#### 3.1 Cache Introduction

Special hooks are provided to support the Pentium OverDrive processor on-chip write back cache and to maintain cache consistency. The external environment can dynamically change the caching policy of the Pentium OverDrive processor on a line by line basis.

The Pentium OverDrive processor has separate code and data caches. Each of the caches are 16 Kbytes in size and each is organized as a 4-way

set associative cache. The data cache follows the MESI cache consistency protocol while the code cache follows a subset of that protocol. For a complete description of the cache see the *Intel486 Microprocessor Family Data Book*(2).

### NOTE:

2. A generic discussion on the operation of cache memories can be found in the Intel Cache Tutorial available from your Intel sales representative or from Intel's Literature department, order #296543-002.

# 3.2 Cache Organization

The Pentium OverDrive processor includes separate code and data caches on chip to meet its performance goals. The code and data caches can be accessed simultaneously. The code cache can provide up to 16 bytes of raw opcodes and the data cache can provide data for two data references all in the same clock. Each of the caches are accessed with physical addresses and each cache has its own TLB (translation look aside buffer) to translate linear addresses to physical addresses. A cache consistency protocol called the **MESI** protocol is implemented in the data cache to ensure data consistency in a multiprocessor environment.

Figure 3-1. Conceptual Organization of Data Cache

Each of the caches are 16 Kbytes in size and each is organized as a 4-way set associative cache. There are 256 sets in each cache, each set containing 4 lines. Each cache line is 16 bytes wide. Replacement in both the data and instruction caches is handled by a pseudo LRU mechanism which requires three bits per set in each of the caches. A conceptual diagram of the organization of the data cache is shown below in Figure 3-1.

The data cache can support two data references simultaneously in one clock, one from each of the two pipelines. It is a write back cache with full support for data consistency in a multimaster environment. This is implemented with two status bits associated with each cache line. The data cache can optionally be configured in write through mode on a line by line basis when in write back cache mode. The storage array in the data cache is single ported but interleaved on 4 byte boundaries to be able to provide data for two simultaneous accesses to the same cache line. The tags in the data cache are triple ported. One of the ports is dedicated to snooping while the other two are used to lookup two independent addresses corresponding to data references from each of the pipelines. The code cache tags are also triple ported. Again, one port is dedicated to support snooping and other two ports facilitate split line accesses (simultaneously accessing upper half of one line and lower half of the next line).

The data cache has a 4-way set associative, 64-entry TLB for 4 KB pages and a separate 4-way set associative, 8-entry TLB to support 4 MB pages. The code cache has one 4-way set associative, 32-entry TLB for 4 KB pages as well as 4 MB pages which are cached in 4 KB increments. The TLBs associated with the instruction cache are single ported whereas the data cache TLBs are fully dual ported to be able to translate two independent linear addresses for two data references simultaneously. Replacement in the TLBs is handled by a pseudo LRU mechanism (similar to the Intel486™ CPU) that re-

quires 3 bits per set. The tag and data arrays of the TLBs are parity protected with a parity bit associated with each of the tag and data entries in the TLBs.

### 3.3 State Transition Tables

Lines cached in the Pentium OverDrive processor can change state because of Pentium OverDrive processor generated activity or as a result of activity on the Pentium OverDrive processor bus generated by other bus masters (snooping). As shown in the following tables, state transitions occur because of Pentium OverDrive processor generated transactions (memory reads/writes) and snooping by the external system. This protocol has minor differences from the MES1 protocol of the Write-Back Enhanced IntelDX2 processor as detailed in Section 10.2.

#### 3.3.1 READ CYCLE

The state transitions for the data cache during reads are shown in Table 3-1. For a cache line that is in the M (Modified), E (Exclusive) or S (Shared) states, the data is transferred from the cache to the core, with no bus cycle generated.

Three different cases can occur when a cache read occurs for an I-state (Invalid) line. An access to an invalid line indicates a miss in the cache, so a read cycle will be generated. If the CACHE# and KEN# pins are sampled low, and WB/WT# is high, then the line will be stored in the E-state in the cache. WB/WT# is sampled with the first BRDY# or RDY# of the transfer, while KEN# is sampled one clock before the first RDY# or BRDY#. If the CACHE# and KEN# are low, and WB/WT# is low. then the cache will be defined as write-through. If PWT is HIGH, cache line fills will always be stored as shared lines, even if WB/WT# is high. This will cause the line to be stored in a S state. If either CACHE# or KEN# is high, then the line is noncacheable, so it will remain in the I state.

PRELIMINARY 17

Table 3-1. Data Cache State Transitions for Pentium® OverDrive® Processor Initiated Unlocked Read Cycles

| Present<br>State | Pin Activity                                                           | Next<br>State | Description                                                                                                                                                                                                                      |

|------------------|------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| М                | n/a                                                                    | М             | Read hit; data is provided to the Pentium OverDrive processor core by cache. No bus cycle is generated.                                                                                                                          |

| Е                | n/a                                                                    | E             | Read hit; data is provided to the Pentium OverDrive processor core by cache. No bus cycle is generated.                                                                                                                          |

| S                | n/a                                                                    | S             | Read hit; Data is provided to the Pentium OverDrive processor by the cache. No bus cycle is generated.                                                                                                                           |

| I                | CACHE# low AND KEN# low AND WB/WT# high AND PWT low                    | Е             | Data item does not exist in cache (MISS). A bus cycle (read) will be generated by the Pentium OverDrive processor. This state transition will happen if <b>WB/WT</b> # is sampled high with first <b>BRDY</b> # or <b>RDY</b> #. |

| l                | CACHE# low<br>AND<br>KEN# low<br>AND<br>(WB/WT# low<br>OR<br>PWT high) | S             | Same as previous read miss case except that <b>WB/WT</b> # is sampled low with first <b>BRDY</b> # or <b>RDY</b> #. If <b>PWT</b> is high, <b>WB/WT</b> # is ignored and the resulting line state is always "S".                 |

| I                | CACHE# high<br>OR<br>KEN# high                                         | I             | <b>KEN</b> # pin inactive; the line is not intended to be cached in the Pentium OverDrive processor.                                                                                                                             |

### NOTE:

The transition from I to E or S-states (based on WB/WT#) happens only if the line is cacheable. If KEN# is sampled high, the line is not cached and remains in the I-state.

### 3.3.2 WRITE CYCLE

The state transitions of data cache lines during Pentium OverDrive processor generated write cycles are illustrated in Table 3-2. Writes to SHARED lines in the data cache are always sent out on the bus along with updating the cache with the write item. The status of the PWT and WB/WT# pins during these write cycles on the bus determines the state transitions in the data cache during writes to S-state lines.

A write to a SHARED line in the data cache will generate a write cycle on the Pentium OverDrive processor bus to update memory and/or invalidate the contents of other caches. If the PWT pin is driven high when the write cycle is run on the bus, the line will be updated, and will stay in the S- state regardless of the status of the WB/WT# pin that is sampled with the first BRDY# or RDY#. If PWT is driven low, the status of the WB/WT# pin sampled

along with the first **BRDY**# or **RDY**# for the write cycle determines what state (E or S) the line transitions to.

The state transition from S to E is the only transition in which the data and the status bits are not updated at the same time. The data will be updated when the cycle is written to the Pentium OverDrive processor write buffers. The state transition does not occur until the write has completed on the bus (last BRDY # or RDY # has been returned). Writes to the line after the transition to the E-state will not generate bus cycles. However, it is possible that writes to the same line that were buffered before the transition to the E-state will generate bus cycles after the transition to E-state.

An inactive **EWBE**# input will stall subsequent writes to an E- or an M- state line until **EWBE**# is returned active.

19

Table 3-2. Data Cache State Transitions for Pentium® OverDrive® Processor Initiated Write Cycles

| Table of El Para Cashe Grate Transmission Foliation Over Divisor Transmission Williams |                               |               |                                                                                                                                                                                                                                                                                             |  |  |  |

|----------------------------------------------------------------------------------------|-------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Present<br>State                                                                       | Pin Activity                  | Next<br>State | Description                                                                                                                                                                                                                                                                                 |  |  |  |

| М                                                                                      | n/a                           | М             | Write hit; update data cache. No bus cycle generated to update memory.                                                                                                                                                                                                                      |  |  |  |

| Е                                                                                      | n/a                           | М             | Write hit; update cache only. No bus cycle generated; line is now MODIFIED.                                                                                                                                                                                                                 |  |  |  |

| S                                                                                      | PWT low<br>AND<br>WB/WT# high | E             | Write hit; data cache updated with write data item. A write through cycle is generated on bus to update memory and/or invalidate contents of other caches. All subsequent writes to E- or M-state lines are held off until completion of write cycle is known and state transition happens. |  |  |  |

| S                                                                                      | PWT low<br>AND<br>WB/WT# low  | S             | Same as above case of write to S-state line except that <b>WB/WT</b> # is sampled low.                                                                                                                                                                                                      |  |  |  |

| S                                                                                      | PWT high                      | S             | Same as above cases of writes to S-state lines except that this is a write hit to a line in a write-through page; status of <b>WB/WT</b> # pin is ignored.                                                                                                                                  |  |  |  |

| ı                                                                                      | n/a                           | I             | Write MISS; a write through cycle is generated on the bus to update external memory. No allocation is done.                                                                                                                                                                                 |  |  |  |

#### NOTE: